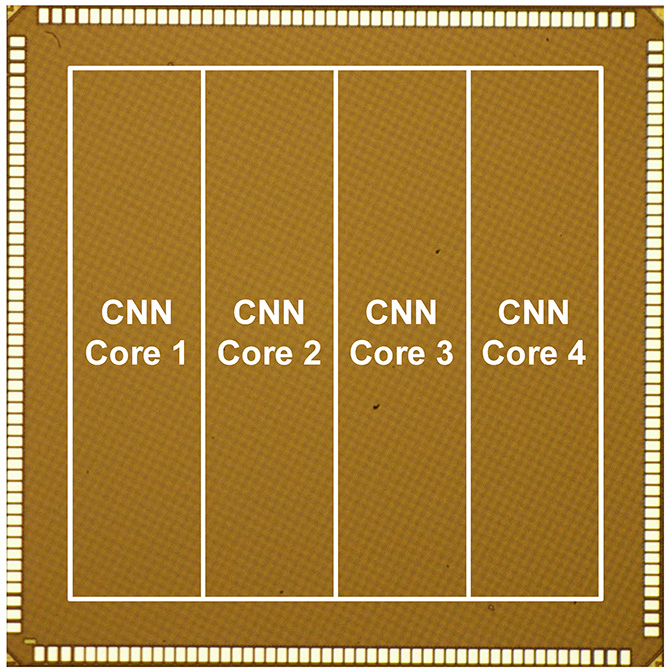

A 1.42TOPS/W Deep Convolutional Neural Network Recognition Processor for Intelligent IoE Systems | |

| - Designer: Jaehyeong Sim in 2016

- Technology: 65nm CMOS - Chip size: 4mm x 4mm - Operating Frequency: 125MHz - Energy-Efficiency: 1.42TOPS/W |

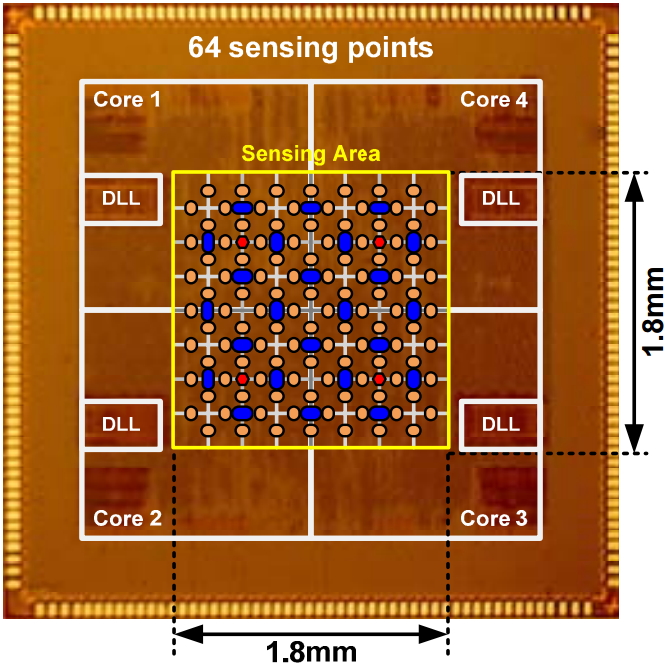

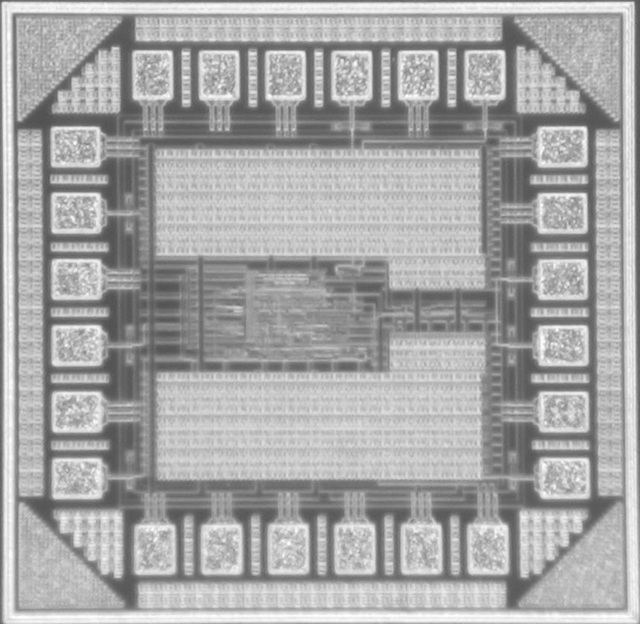

All-digital hybrid temperature sensor network for dense thermal monitoring | |

| - Designer: Seungwook Paek in 2013

- Technology: 0.13um CMOS - Chip size: 4mm x 4mm - Sensing Area: 1.8mm X 1.8mm - Operating Frequency: 100MHz(HTSN), 400MHz(TMU) |

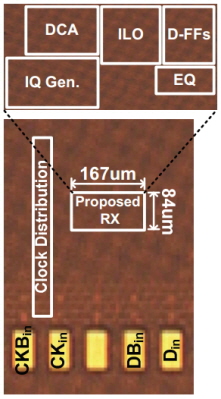

A 12Gb/s 0.92mW/Gb/s Forwarded Clock Receiver based on ILO with 60MHz Jitter Tracking Bandwidth Variation Using Duty Cycle Adjuster in 65nm CMOS | |

| - Designer: Young-Ju Kim in 2013

- Technology: 65nm CMOS - Die size: RX 167um x 84um - Data Rate: 12Gb/s - Jitter Tracking Bandwidth: 760MHz - Power consumption : 11mW |

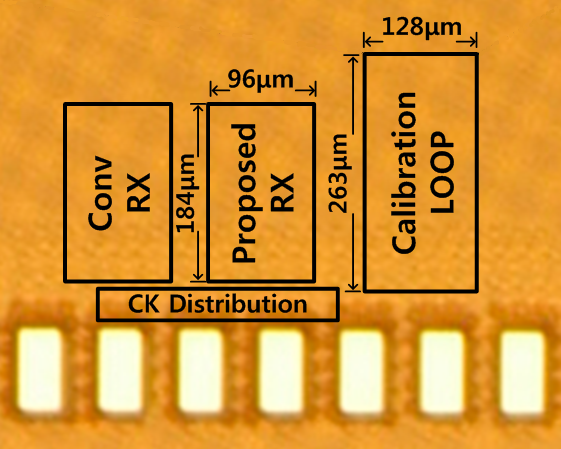

A 1.22mW/Gb/s 9.6Gb/s Data Jitter Mixing Forwarded-Clock Receiver Robust against Power Noise with 1.92ns Latency Mismatch between Data and Clock in 65nm CMOS | |

| · Designer: Sang-Hye Chung in 2012

· Technology: 65nm CMOS · Die size: RX: 96um x 184um Calibration Loop: 128um x 263um · Data Rate: 9.6Gb/s · RX Power Efficiency: 1.22mW/(Gb/s) |

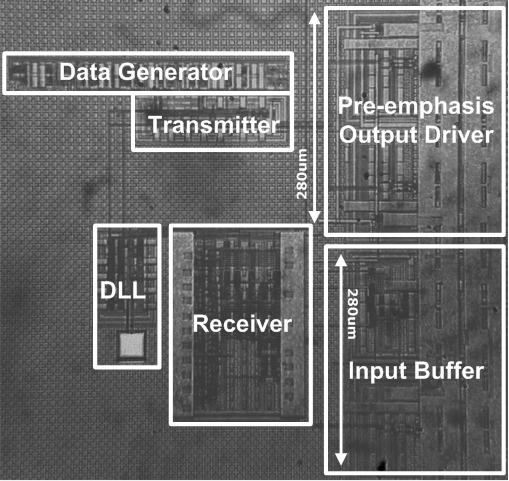

An 8Gb/s Forwarded-Clock I/O Receiver with up to 1GHz Constant Jitter Tracking Bandwidth Using a Weak Injection-Locked Oscillator in 0.13um CMOS | |

| · Designer: Sang-Hye Chung in 2011

· Technology: 0.13um CMOS · Die size: 150um x 280um · Data Rate: 8Gb/s · Jitter Tracking Bandwidth: 70M~1GHz · Power consumption : 17.2~21.4mW |

A 1mJ/frame Unified Media Application Processor with a 179.7pJ Mixed-Mode Feature Extraction Engine for Embedded 3D-Media Contents Processing | |

| · Designer: Hyo-Eun KIM in 2012

· Technology: 90nm CMOS(1P8M) · Die size: 4mm x 4mm · Operation frequency : 100MHz · Power consumption : 133mW-2D AR(analog) 198mW-2D AR(digital) 253mW-3D-view AR |

A 275mW Heterogeneous Multimedia Processor for IC Stacking on Si-interposer | |

| · Designer: Hyo-Eun KIM in 2011

· Technology: 0.13um CMOS · Die size: 4mm x 4mm · Operation frequency : 200MHz · Power consumption : 275mW |

An Adaptive Equalizer with the Capacitance Multiplication for DisplayPort Main Link in 0.18 μm CMOS Logic Process | |

| · Designer: Won-Young LEE in 2011

· Technology: 0.18um CMOS · Die size: 0.11mm^2 · Energy / bit : 8.3pJ/bit |

A Mobile 3-D Display Processor With A Bandwidth-Saving Subdivider | |

| · Designer: Seok-Hoon KIM in 2011

· Technology: 0.13um 1P6M CMOS · Operation frequency : 50MHz · Power consumption : 140mW |

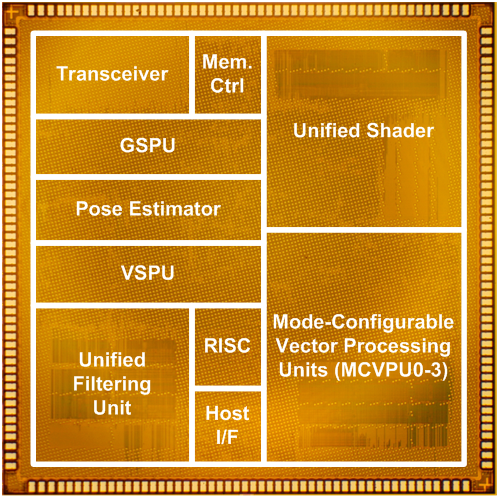

A Graphics and Vision Unified Processor with a 0.89uWfps Pose Estimation Engine for Augmented Reality | |

| · Designer: Jae-Sung YOON in 2010

· Technology: 0.18um CMOS · Die size: 5mm x 5.75mm · Operating Frequency : 200MHz · Power consumption : 413mW |

A Data Pattern-Tolerant Adaptive Equalizer Using Spectrum Balancing Method | |

| · Designer: Hye-Yoon JOO in 2010

· Technology: 0.18um CMOS · Die size: 2.4mm x 1.7mm · Performance: 6.4Gb/s · Power consumption : 85mW |

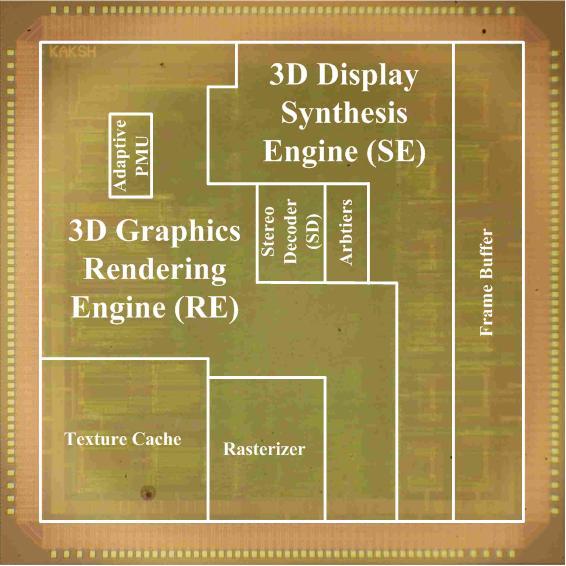

A 116 fps74 mW HETEROGENEOUS 3D-MEDIA PROCESSOR FOR 3-D DISPLAY APPLICATIONS | |

| · Designer: Seok-Hoon KIM in 2009

· Technology: 0.13um CMOS · Die size: 5mm x 5mm · Performance: 60MHz & 152MHz · Power consumption : 74mW / 198mW |

100MHz-to–1GHz open-loop ADDLL with fast lock-time for mobile applications | |

| · Designer: Mi-Jo KIM in 2010

· Technology: 0.18um CMOS · Die size: 0.21mm^2 · Performance: 100M~1GHz · Power consumption : 64mW |

Tessellation-Enabled Shader II | |

| · Designer: Kyusik Chung in 2008

· Technology: 0.18um 1P4M CMOS · Die size: 4.95mm x 5.75mm · Performance: 120Mvertices/s @ 100MHz, 1/250 BW saving |

A 6Gb/s/pin Pseudo-Differential Signaling Using Common-Mode Noise Rejection Techniques without Reference Signal for DRAM Interfaces | |

| · Designer: Kyung-Soo Ha in 2008

· Technology: 0.18um CMOS · Data rate: 6Gbps · Power Consumption: 242.5mW |

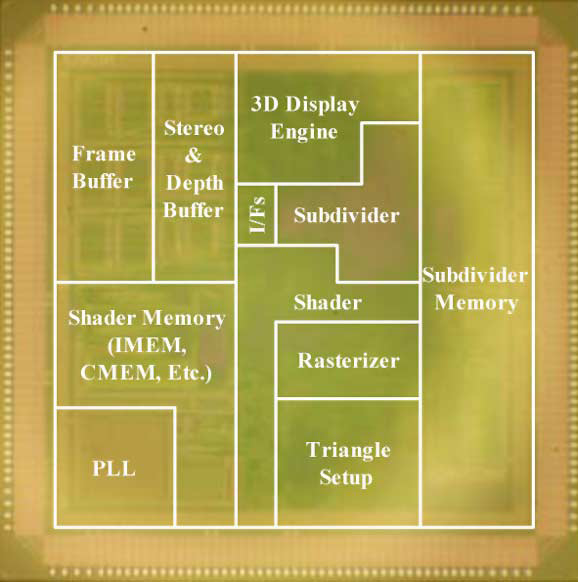

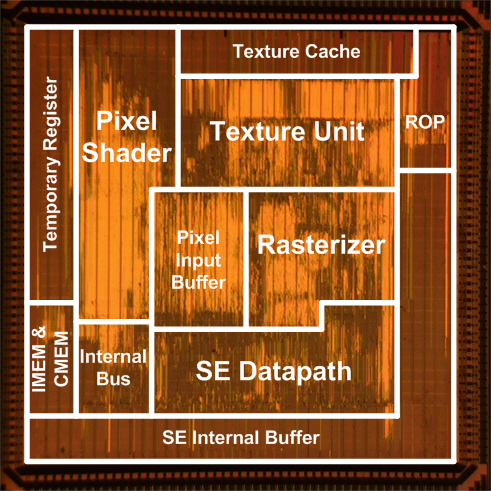

A 116fps 74mW Mobile 3D Display Processor | |

| · Designer: Seok-Hoon Kim in 2008

· Technology: 0.13um CMOS · Supply Voltage: 3.3V · Frequency: 60Mhz (Overall) & 152Mhz(SE) · Performance: 49fps decoding rate, 480Mtexels/s texturing rate,116fps 3D image synthesis rate · Power consumption:198mW (full processing) 74mW (video processing + 3D display processing) 36mW~165mW (3D graphics rendering + 3D display processing) |

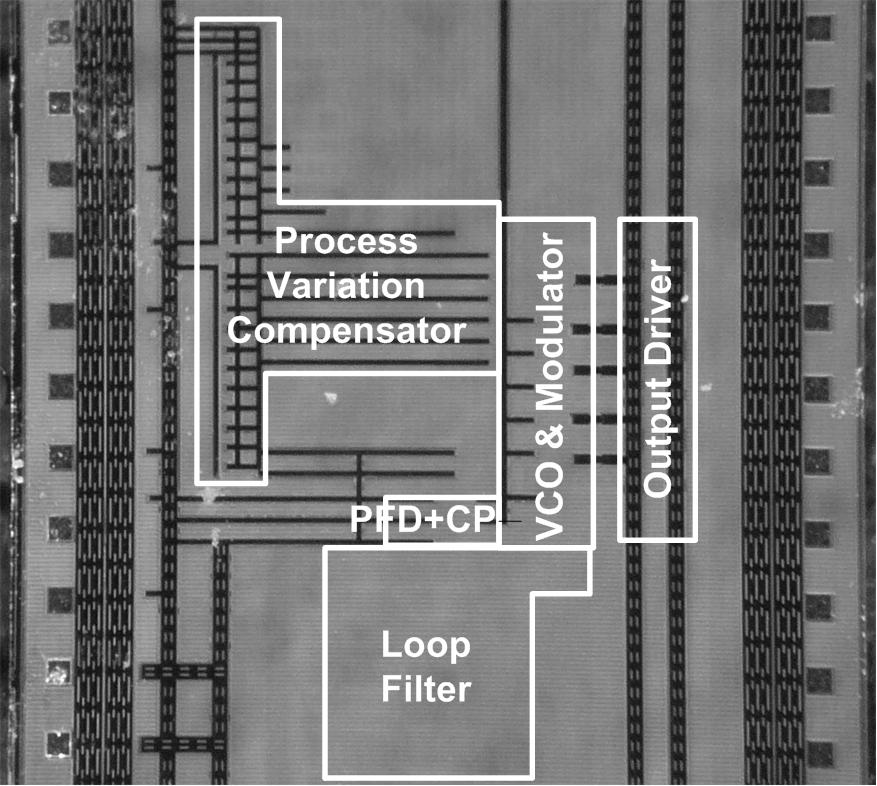

A Spread Spectrum Clock Generator with Spread Ratio Error Reduction Scheme for DisplayPort Main Link | |

| · Designer: Won-Young Lee in 2008

· Technology: 0.18um CMOS · Supply Voltage: 1.8V · Chip Size: 1.9mm X 0.96mm · Output clock frequency: 10-phase 270 MHz / 162 MHz · Power Consumption: 19 mW @ 270 MHz with output drivers · Spread ratio: 5000 ppm down-spread · Peak reduction: 8.75 dBm |

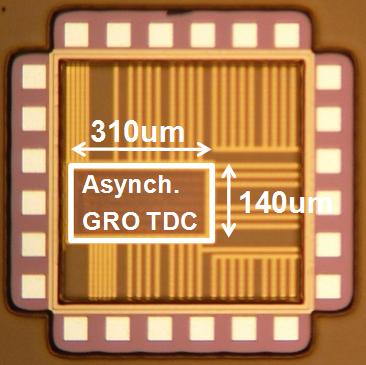

An Area Efficient Asynchronous Gated-Ring Oscillator Time-to-Digital Converter | |

| · Designer: Kyudong Hwang in 2008

· Technology: 0.18um CMOS · Supply Voltage: Core(1.8V), I/O(3.3V) · Resolution: 30ps (with 80ps raw resolution) · Power consumption: 4mW ~ 10mW · Active area: 0.14mm x 0.31mm |

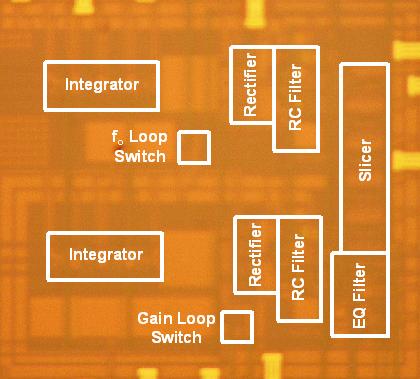

A Data Pattern-Tolerant Adaptive Equalizer Using Spectrum Balancing Method | |

| · Designer:Hyeyoon Joo in 2008

· Technology: 0.18um CMOS · Supply Voltage: 1.8V · Maximum data rate: 6.4Gb/s · Power Consumption: 85mW (Equalizer), 135mW (Tx,I/O) · Active area: 0.63mm x 0.55mm |

3.2-Gb/s Transceiver with a Quarter-Rate Linear Phase Detector reducing the phase offset | |

| · Designer:Kyung-Soo Ha in 2007

· Technology: 0.18um CMOS · Supply Voltage: 1.8V · Power Consumption: PLL (9-mW), Tx (27-mW), Rx (45-mW), I/O (144-mW) · Input data rate range: 1.6-Gb/s ~ 3.2-Gb/s |

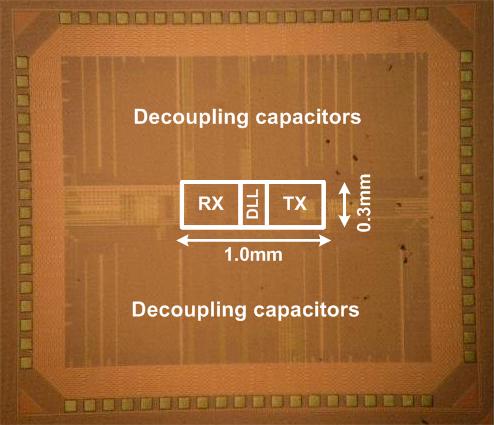

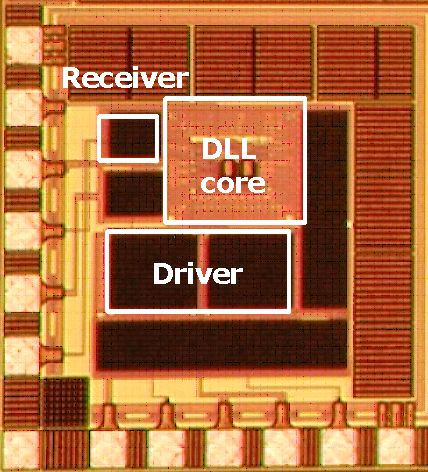

A 3.2-Gbps/pin transceiver for DDR memory interface with a low-jitter digital DLL and a MUX embedded pre-emphasis circuit | |

| · Designer: Kwang-Il Oh in 2007

· Technology: 0.18um CMOS · Supply Voltage: 1.8V · External Clock Frequency: 800MHz · Data Rate: 3.2Gbps · Power Consumption: 50mW/Ch [Tx] 30mW/Ch [Rx] 12mW [DLL] |

Tessellation-Enabled Shader | |

| · Designer: Kyusik Chung in 2007

· Technology: 0.18um 1P4M CMOS · Performance: 120Mvertices/s @ 100MHz · Die Size: 4.95mm X 5.75mm |

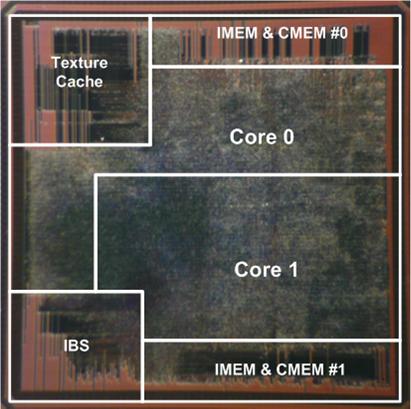

Two-Core Dual-Issue VLIW Unified Shader for 3D Graphics | |

| · Designer: Jae-Sung Yoon in 2007

· Technology: 0.18um CMOS · Supply Voltage: 1.8V · Chip Size: 4.5mm X 4.5mm · Operating Frequency: 143MHz · Power Consumption: 367mW · Transistor Counts: 3.4M logic, 14KB on-chip SRAM · Supported Shader Standard: OpenGL ES 2.0 Shader Model 3.0 · Vertex Shading Performance: 143Mvertices/s (Geometry Transformation) · Piexel Shading Performance: 2.3Gtexels/s (Trilinear Filtering) |

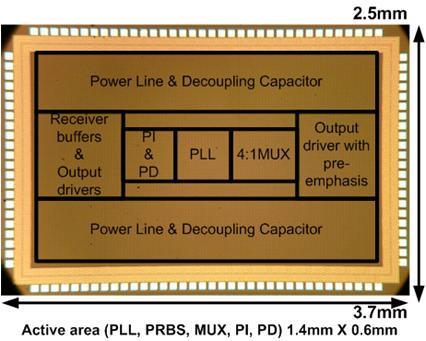

A 3.2Gbps/pin transceiver for DDR memory interface with 4:1 MUX embedded pre-emphasis circuit | |

| · Designer: Kwang-Il Oh in 2006

· Technology: 0.18um CMOS · Supply Voltage: 1.8V · Data Rate: 3.2Gbps (800MHz ext. clock) · Power Consumption: 30mW/ch (Tx), 50mW/ch (Rx), 6mW (DLL) · Core size: 680 um x 600 um |

A 36 fps SXGA 3D Display Processor with a Programmable 3D Graphics Rendering Engine | |

| · Designer: Seok-Hoon Kim in 2006

· Technology: 0.18um CMOS · Supply Voltage: 1.8V · Frequency: 50MHz (3D image synthesis rate:36fps Texturing rate : 400Mtexels/s) · Power Consumption: 379mW · Core size: 5mm x 5mm |

A DLL with Jitter-Reduction Techniques for DRAM Interfaces | |

| · Designer: Byung-Guk Kim in 2006

· Technology: 0.13um CMOS · Supply Voltage: 1.2V · Power Dissipation: 6mW · Operating Range: 300MHz - 1GHz |

A 20Gb/s 1:4 DEMUX without Inductors in 0.13um CMOS | |

| · Designer: Byung-Guk Kim in 2005

· Technology: 0.13um CMOS · Supply Voltage: 1.2V · Power Dissipation: 210mW · Die Area: 1050um x 920um |

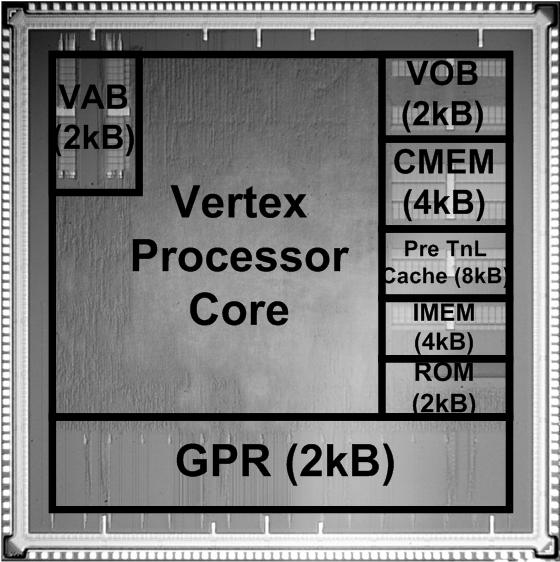

A 120Mvertices/s Multi-threaded VLIW Vertex Processor for Mobile Multimedia Applications | |

| · Designer: Chang-Hyo Yu in 2005

· Technology: 0.18um CMOS · Supply Voltage: 1.8V · Frequency: 100MHz · Power Consumption: 157mW · Core Size: 4.0mm x 4.0mm |

A 500MHz DLL with Second Order Duty Cycle Corrector for Low Jitter | |

| · Designer: Byung-Guk Kim in 2004

· Technology: 0.13um CMOS · Supply Voltage: 1.2V · Lock Range: 140MHz ~ 780MHz · Jitter: 3.8ps RMS, 29.2ps pk-to- pk · Power Dissipation: 4mW · Output Duty Error: < ±1.6% for input duty error < ±25% |

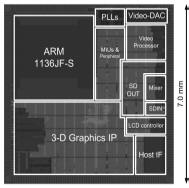

A 1.3 Gtexels/s 3D Graphics SoC for Consumer Applications | |

| · Designer: Donghyun Kim in 2004

· Technology: 0.13um CMOS · Core Size: 7.0mm x 7.1mm · Supply Voltage: 1.2V · Frequency: 166MHz · Power: 407mW for fully activated 3-D Graphics IP |

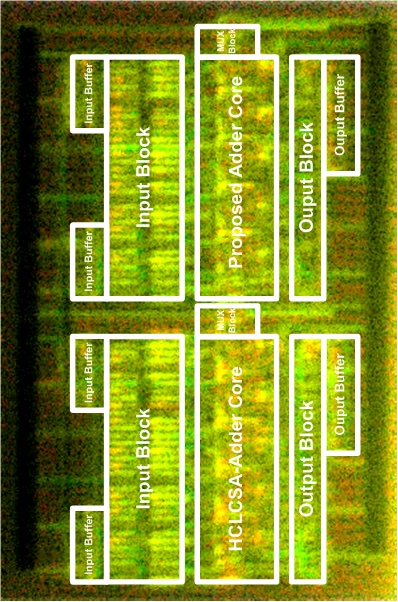

A Low Power Hybrid Adder using Single-stage Multiplexer Circuits | |

| · Designer: Chi-Yeon Kim in 2004

· Technology: 0.18um CMOS · Core Size: 260um x 520um · Supply Voltage: 1.8V · Frequency: 1.22GHz · Power: 16.3mW @1GHz |

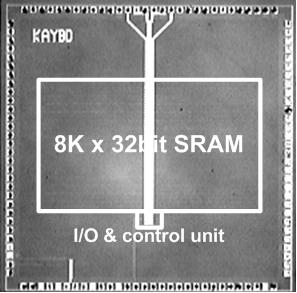

A low power SRAM using hierarchical bit lines and local sense amplifiers | |

| · Designer: Byung-Do Yang in 2004

· Technology: 0.25um CMOS · Core Size: 6.13mm2 (3.26mm x 1.88 mm) · Organization: 8K x 32bits · Supply voltage: 2.5V · Frequency: 220MHz · Power dissipation: 28mW(@write), 26mW(@read) |

A low power ROM using single charge-sharing capacitor | |

| · Designer: Byung-Do Yang in 2004

· Technology: 0.25um CMOS · Core Size: 0.27mm2(393um x 680um) · Organization: 4K x 32bits (512 word lines x 256 bit lines) · Supply Voltage: 2.5V · Frequency: 240MHz · Power: 8.2mW @240MHz |

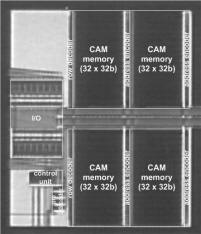

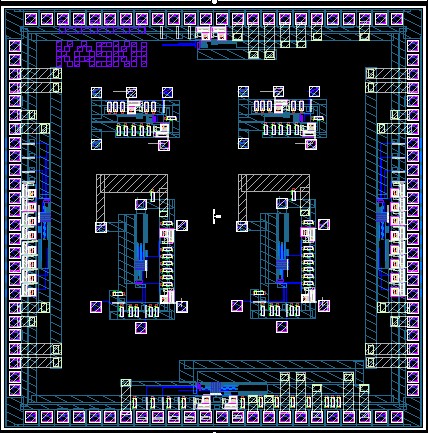

A low power CAM using the pulsed NAND-NOR match-line and charge-recycling search-line | |

| · Designer: Byung-Do Yang in 2004

· Technology: 0.25um CMOS · Core Size: 0.32mm2(0.51mm x 0.62mm) · Organization: 128 x 32bits · Supply voltage: 2.5V · Frequency: 260MHz · Energy/bit/search: 17.2fJ |

A Low Power SRAM with Elevated Source Level Cells | |

| · Designer: Byung-Do Yang in 2003

· Technology: 0.25um CMOS · Core Size: 2.96ⅹ1.86mm2 · Supply Voltage: 2.5V · Frequency: 330MHz · Power: 66mW(write), 43mW(read) @300MHz · Organization: 8Kⅹ32bits |

All-digital fast-locking clock-deskew buffer using a hierarchical phase locking delay | |

| · Designer: Kihyuk Sung in 2003

· Technology: 1poly 4metal hynix 0.3um CMOS · Core Size: 655ⅹ120um2 · Supply voltage: 3.3V · Frequency: 142MHz ~ 200MHz · Power dissipation: 56mW(@200MHz) |

Reduced Clock Swing Dual Edge Triggered Flip-Flop | |

| · Designer: Kwangil Oh in 2003

· Technology: 1 poly 5 metal, anam 0.25um CMOS · Chip Size: 300umⅹ200um · Supply voltage: 2.5V · Frequency: 500MHz · Power dissipation: 44.5mW(@500Mhz) |

A 250MhHz - 2GHz Wide Range Delay-Locked Loop | |

| · Designer: ByungGuk Kim in 2003

· Technology: 0.18um CMOS process · Chip size: 230umⅹ 230um(core) · Frequency: 250MHz ~ 2GHz · Supply Voltage: 1.8V · Power Dissipation: 6.46mW@2GHz |

Edge Function Based Anisotropic Texture Filtering Hardware | |

| · Designer: HyunChul Shin in 2003

· Technology: 0.35um CMOS · Core Size: 3ⅹ3mm2 · Chip Size: 5ⅹ5mm2 · Supply Voltage: 3.3V · Frequency: 100MHz · Feature: 100M texture-filtered Color values/sec or 3.33M texture-filtered Triangles/sec @100MHz |

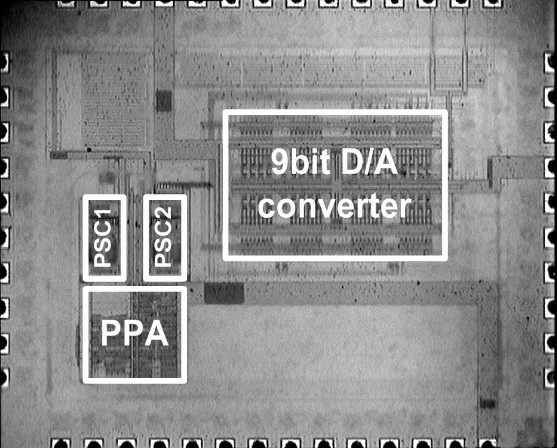

An 800MHz Low Power Direct Digital Frequency Synthesizer with an On-Chip D/A Converter | |

| · Designer: Byung-Do Yang in 2001

· Technology: 0.35um CMOS · Chip size: 1.30mm2 · Frequency: 820MHz@3.3V · Supply Voltage: 3.3V · Power Dissipation: 174mW@800MHz(3.3V) · Tuning Latency: 26 clock cycles · Frequency Resolution: 0.186Hz@80 |

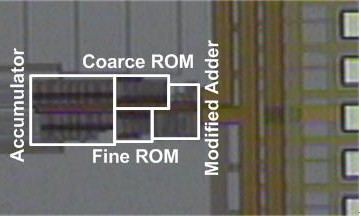

A Direct Digital Frequency Synthesizer Using A New ROM Compression Method | |

| · Designer: Byung-Do Yang in 2000

· Technology: 0.35um CMOS · Chip Size: 550ⅹ220um2 · Tuning Latency: 11 clock cycles · Supply voltage: 3.3V · Frequency: 500MHz · Power dissipation: 9.56mW@100MHz(3.3V) · Frequency Resolution: 0.1164Hz(at 500MHz Fclk) |

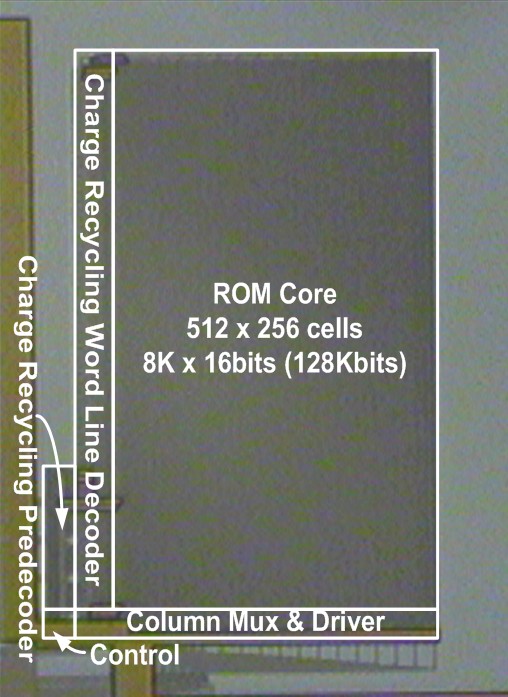

A Low Power ROM using Charge Recycling and Charge Sharing Techniques | |

| · Designer: Byung-Do Yang in 2000

· Technology: 0.35um CMOS · Core Size: 0.62ⅹ0.83mm2 · Frequency: 120MHz · Supply Voltage: 3.3V · Organization: 8Kⅹ16bits ROM · Power: 8.63mW@100MHz |

A Single-Pass Antialiased Rasterization Processor | |

| · Designer: Jinaeon Lee in 1999

· Technology: 0.35um 3 metal EML · Chip Size: 7ⅹ7mm2 · Frequency: 100MHz · Supply voltage: 3.3V · Feature: 20Mbit SDRAM for PB, 69Kbit(512*138bit) SRAM for FB, 28.9M fragments/sec or 0.96M triangles/sec@100MHz |

Multiport SRAM for video applications | |

| · Designer: Cheonho Bae in 1999

· Technology: 0.6um CMOS · Frequency: 100MHz · Supply Voltage: 3.3V · Feature: A proposed embedded eight-port SRAM has an ability to access 8 by 8 video data format efficiently |

High-Speed and Low-Swing On-Chip Bus Interface Using Threshold Voltage Swing Driver and Dual Sense Amplifier Receiver | |

| · Designer: Byung-Do Yang in 1999

· Technology: 0.6um CMOS · Chip Size: 4ⅹ4mm2 · Frequency: 500MHz · Feature: a new high-speed and low-swing on-chip bus interface using Threshold Voltage swing driver and DSA receiver |

A 250MHz Low Voltage Swing Bus Driver for Embedded Memory Logic | |

| · Designer: Hosoek Lee in 1998

· Technology: 0.8um CMOS · Frequency: 250MHz · Supply Voltage: 3.3V · Feature: The proposed driver controls the bus swing voltage within a few hundreds of mV , and dissipates only 1/4 of power compared to GTL. |

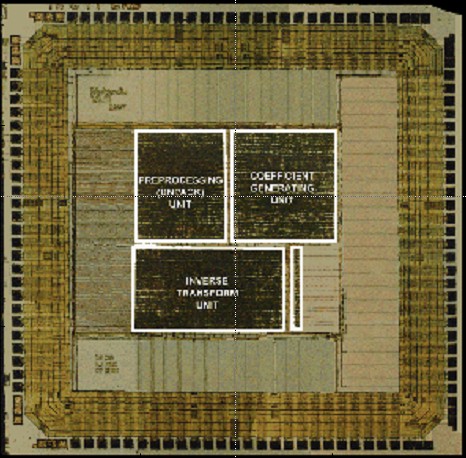

Fractal Image Decoder | |

| · Designer: Chun-Ho Kim in 1998

· Technology: 1 poly 3 metal, 0.6um CMOS · Chip Size: 4mmⅹ4mm · I/O pin number: 80 pins · Supply voltage: 3.3V · Frequency: 40MHz · Power dissipation: 9.5mW@3.3V · Decoding Speed: 63 frame/sec |

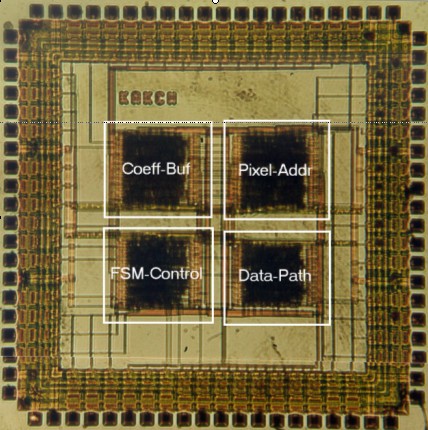

VLSI Implementation of Decoder for Decompressing Fractal-based Compressed image | |

| · Designer : Kyunghoon Kim in 1997

· Technology : 1 poly 3 metal, 0.6um CMOS · Core Size : 2.5ⅹ2.5mm2 · Chip size : 5ⅹ5mm2 · Frequency : 50MHz · Supply Voltage : 5V · Power dissipation : 210mW@5V |

Fast Phong Shader | |

| · Designer : HyunChul Shin in 1997

· Technology : 0.8um CMOS · Core Size : 3.5ⅹ3.5mm2 · Chip size : 5ⅹ5mm2 · Supply voltage : 5V · Frequency : 87MHz · Feature : 87M phong-shaded color values/sec or 29M phong-shaded Triangles/sec @87MHz |

IEEE754 Compatible Floating Point Unit | |

| · Designer : Yunseok Choi in 1997

· Technology : 0.8um 1 poly 1 metal CMOS · Core Size : 2.47ⅹ2.80mm2 · Chip Size : 5mmⅹ5mm · Frequency : 100MHz · Supply Voltage : 5V · I/O pin : 100 pins |