| Display Interface |

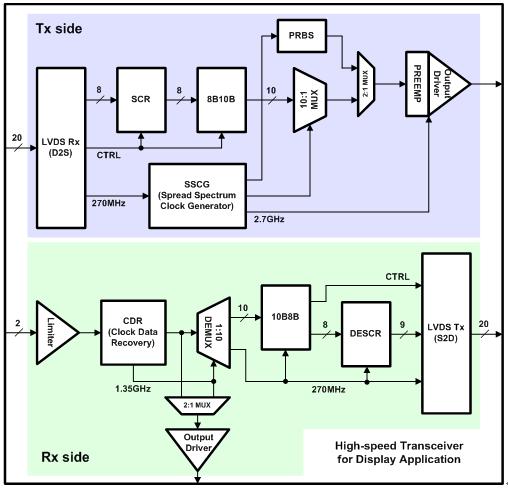

We are developing the transceiver circuit for the data interface between the graphic processor in the computer and the timing controller in the flat panel display device. Conventional display data interface like LVDS or TMDS can support several hundred of Mbps data rate. But, as the demand for the larger resolution and deeper color depth of the flat panel display is increased, new standards like DisplayPort, HDMI are emerged as the display interface which can support several Gbps data rate. We analyzed the channel environment and proposed the transceiver circuits for these display interfaces. The transceiver consists of logic component like scrambler-descrambler, 8B10B encoder/decoder and the high-speed mixed-mode circuit like 10:1 MUX/DEMUX, Pseudo random binary sequence(PRBS) generator, Spread-spectrum Clock Generator(SSCG), Clock and data recovery circuit, Output Driver with Pre-emphasis and Input Limiter, etc..