| Energy-Efficient Multimedia Application Processor |

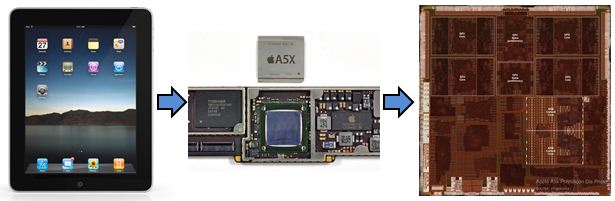

Application Processor (AP) is the main chip on today's handheld devices such as smartphones or tablet PCs. Unlike PC-based system, several limitations exist on embedded environment; battery (power), resource (area), and bandwidth limitations. Based on the heterogeneous many-core platform which includes various functional IPs on a single silicon die, power dissipation, implementation area, and memory bandwidth should be carefully considered in AP design. Among the heterogeneous functional IPs on AP, we focused on programmable accelerators for multimedia applications such as GPU, ISP, and DSP which are responsible for intensive multimedia workloads in AP.

Multimedia applications can be classified into two types; 2-dimensional (2-D) image analysis applications such as image processing or computer vision and 3-D image synthesis applications such as 3-D graphics. Based on the system which can accommodate those 2-D/3-D image analysis/synthesis applications, more complex multimedia contents such as augmented reality (AR), 3D display, and 3-D reconstruction can be processed on the same platform. Media contents processing includes both data-intensive memory operations and compute-intensive non-memory operations. In order to support various media applications on mobile platform, both operations should be supported in energy-efficient way.

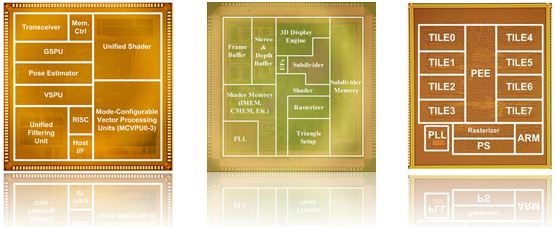

We design a heterogeneous multimedia processor (media application processor; MAP) for media contents processing on mobile devices. It includes reconfigurable hardware components such as a data transceiver with reconfigurable output drivers, a multi-purpose micro-operation cache, and mode-configurable parallel processing cores for general-purpose media contents processing on energy-limited embedded environment. The data transceiver and the multi-purpose micro-operation cache support data-intensive memory operations, while the mode-configurable parallel processing cores support compute-intensive non-memory operations.